概述和功能介绍

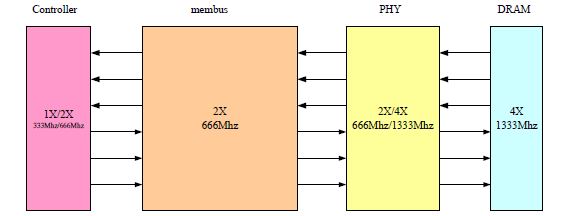

This memory controller supports DDR3/4 SDRAM. DDR3/4 memory controller is a high-speed interface used for data read/write between internal engine and outside SDRAM bus, and transfers the internal signal to meet the SDRAM specification. The DDR IP is compliant with the latest JEDEC standards and is silicon proven

The DDR3/4 memory controller includes several Sub-Arbiters , Main-Arbiter and Controller module. Sub-Arbiter supports 4 masters. Sub-Arbiter would be placed in partition or in memory controller. Main-Arbiter supports 16 masters. The memory arbiter will do arbitration one all the masters’ (internal engines) request and send those request to DDR (Double Data Rate) controller. The DDR (Double Data Rate) controller will convert the internal request to DRAM chip protocol for data read/write. The DDR controller also implements the DRAM refresh, DRAM dynamic power down, DRAM Scramble and DRAM Private Usage functions.

功能描述

-

Support s DDR 4 /DDR3 SDRAM

-

16 bit s width , Single Channel DDR 4 /DDR3 SDRAM Interface .

-

16 bits for per channel, could support 2 x8 bits DDR3, but could not support 2 x8 bits DDR4.

-

Memory Clock up to 6 66 MHz, DFI Clock up to 666 MHz .

-

Support DDR3 800/1066/1333/1600 /1866/2133; DDR 4

-

1866/2133/2400/2666.

-

Support s Continuous Request

-

Supports independent Single channel Arbiter and Controller: s eparate registers to 4 registers: Should use 32bits System Reg in N OC

-

Support SW DDR training

-

Support DDR IO loopback test

-

Controller features:

-

Support s I MB3.0

-

MEM_CLK : DIMM Data rate = 1:4 Protocol

-

Support s Dynamic Enter and Exit DDR3/4 Power Down Modes (internal use)

-

Supports Out of Range interrupt

-

Supports 64 MB 2 GB total DRAM size

-

Programmable refresh cycle

-

Support Dynamic ODT function.

-

Support s memory scramble 3.0 (Scramble Full Memory Space)

-

Supports Memory Private Usage function

-

Supports Video Frame Buffer protection function

-

Support TrustZone Function (13 memory

-

Supports monitor 2 memory space write operation. (internal use)

-

Support store DDR3/4 MR value (internal use)

-

Support s DDR 3/4 Self Refresh function

-

Supports DDR4 Fine Granularity Refresh Mode (internal use)

-

Supports DDR4 DBI/DM

Benefits

-

DDR Controller IP functionality is verified in NC-Verilog simulation software using test bench written in

-

Verilog HDL

-

High performance

-

Low power

-

Low gate count

-

Highly flexible, scalable, configurable

-

Ease of integration

Applications

-

Automotive,

-

Application Processors,

-

Digital Baseband Modems,

-

Set-Top-Box,

-

Digital TV,

-

OTT,

-

Surveillance,

-

IoT, Enterprise

-

SSD Controllers

![]()