概述和功能介绍

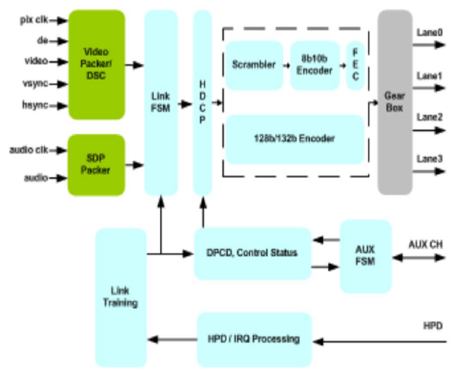

DP Tx控制器IP符合显示端口v2.0规范。这个IP具有兼容性,能够为低版本设备提供简单的接口。DP v2.0 Rx控制器IP已在FPGA环境中通过硅验证验证。DP的主机接口可以是简单的接口,也可以是AMBA APB、AMBA AHB、AMBA AXI、VCI、OCP、Avalon、PLB、倾斜链接、Tilelink, Wishbone 或自定义协议等.

功能描述

-

符合DP 2.0版本的规范。

-

支持全显示端口发射器功能

-

支持多车道模式,最多4车道

-

支持10bit、20bit、40bit和80bit的并行接口

-

支持每时钟1/4/8/16像素

-

支持框架中的控制符号(默认和增强框架模式)

-

支持交错和非交错视频流

-

支持缝隙间隙(ECC)

-

支持主链路、辅助链路和热插拔功能

-

支持快速链接和全链接培训

-

支持跳过链接训练

-

支持通过AUX CH和EDID的I2C。

-

支持符号填充和传输单元

-

支持3D立体声和支持面板重放

-

支持ANSI8B10B编码

-

支持128b/132b通道编码

-

支持所有显示端口中提到的视频格式,直至2.0版本

-

支持显示端口中提到的所有二级数据包格式,直到2.0版本。

-

支持基于HPD的链接训练

-

支持 RGB、YCBCR444、YCBCR422、YCBCR420、YOnly 和 RAW 色彩格式。

-

支持SST和MST模式的分裂SDP

-

支持IEC 60958-1, IEC 60958-3, IEC 60958-4, IEC 61937-1, IEC 61937-3, CEA/CTA 861-F, 861-G中提到的所有音频格式。

-

支持训练模式序列(TPS2, TPS3, TPS4)。

-

支持显示端口规范中的加扰器

-

扰频器可以动态地启用或禁用

-

支持每512个符号后重置加扰器

-

支持多流传输(MST)操作

-

支持高级链路电源管理,以减少唤醒延时

-

支持基于GTC的视频定时同步

-

支持显示流压缩(DSC),最高版本为1.2a

-

支持高达2.3版的高带宽数字内容保护系统(HDCP v2.3)。

-

支持完全认证

-

支持绕过认证

-

支持水平消隐扩展

-

支持10、13.5和20Gbps/lane链接速率的超高比特率

交付件

-

显示端口接收器接口IP可以以源代码和网表的形式提供给客户

-

源代码可以以Verilog语言格式的文本提供给客户,如果客户需要VHDL,SystemC语言格式的文本也可以提供

-

容易使用的Verilog测试环境及Verilog语言编写的测试用例

-

Lint、CDC、综合、仿真脚本以及配套的Waiver文件

-

根据IP-XACT RDL 产生的寄存器地址列表

-

固件代码和Linux驱动文件包

-

交付文档包括用户指南和版本手册

![]()