概述和功能介绍

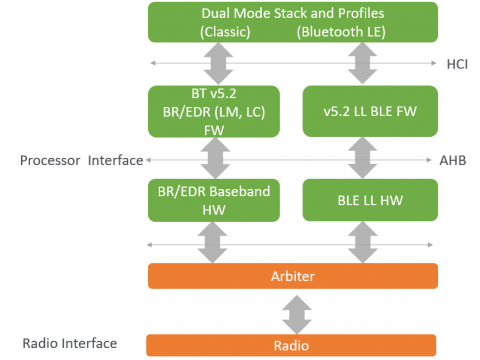

复合HW和FW的基带控制器IP核符合经典蓝牙规范和蓝牙低功耗v5.3规范.

与标准蓝牙的HCI兼容的IP设计,使它能和任何一款蓝牙双模5.3主机软件协议栈及相关开发套件一起使用,对HCI的拆分便于下层和上层可以在不同的处理器或系统上运行,也可以组合在同一处理器上运行,从而形成完全托管的解决方案。支持耳机的解决方案,包括TWS的功能.

-

将支持2个连接电源考虑事项

-

IP将提供挂钩,以确保SoC中的节能机制

-

电源门控、时钟门控和在睡眠期间保持低功率域是基本的挂钩

-

将支持基于协议的功能,如自适应窗口加宽和从属延迟。

-

IP始终被设计为将RF的正常运行时间降至最低

功能描述

-

软件内存占用(ARM Cortex M0/M3):ROM~300KB;内存~112 KB

-

组合硬件门计数:250 k门

-

仲裁逻辑由硬件实现,并由软件辅助

-

基带和LE LL加速器

-

发现/连接/角色切换程序

-

LE广告/扫描/连接程序

-

基带级流控制、ACK处理和重传

-

省电:休眠模式-核心硬件模块的时钟关闭,时钟和电源管理模块除外。

-

深度睡眠模式-时钟关闭所有模块。蓝牙时钟保持在32KHz域中。外部RF调制解调器芯片也可以关闭。

-

关机–整个基带时钟可以通过固件关机。外部RF调制解调器芯片也可以关闭。启用电源门控。

可交付成果

-

可合成Verilog RTL

-

行为模型

-

模块测试台和测试用例

-

ASIC和FPGA合成脚本

-

BlueWiz FPGA平台

-

Flash下载实用程序

-

HCI指挥官–HCI应用

-

BlueWiz架构文档

-

BlueWiz验证文件

-

SoC集成方法说明

-

开发工具用户手册

-

C语言的HCI/LM/LC/LL固件源代码

-

传输驱动程序(UART、USB)

-

开发平台的平台驱动因素

-

MINT OS/FreeRTOS的OSAL

好处

-

最小MIPS:硬件在其当前状态下维持链路,因此固件开销仅用于PDU和数据交换。硬件还支持所有类型的逻辑链路

-

最大中断延迟容差

-

最小中断处理时间:时间关键和非时间关键功能的划分。使用MINT OS任务架构在任务上下文中处理非时间关键功能

-

高效的硬件/软件分区:减少固件和硬件之间的交互。减少公交车活动

-

有源和低功耗模式时钟门控

-

固件和硬件可测试性:通过供应商命令访问关键固件数据结构、较低层(如LMP)以绕过正常功能路径、BB寄存器

-

记录器:实时转储固件、基带和RFIC状态。固件中嵌入的断言日志

应用

-

智能手机

-

耳机、耳机、扬声器

-

平板电脑

-

游戏

-

远程控制

![]()