概述和功能介绍

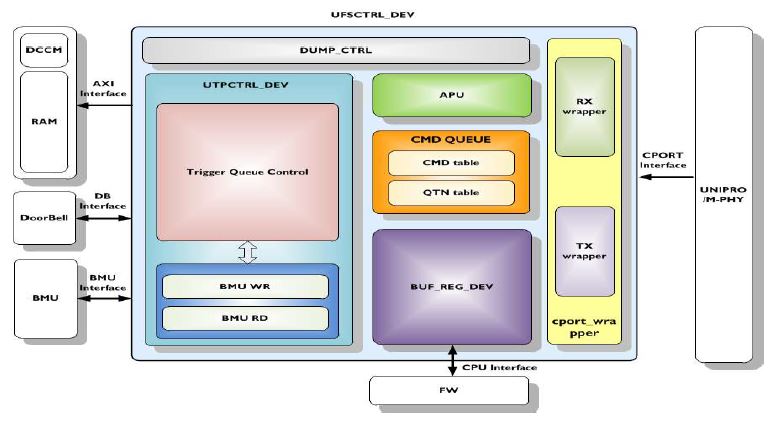

通用闪存(UFS)控制器IP符合最新的JEDEC UFS v3.1规范。UFS是高性能、低功耗的串行接口,可以有效地在主机处理器和大容量存储设备之间移动数据。

客户的产品设计师能够用UFS控制器IP与内部开发的UniPro控制器IP和M-PHY IP轻松地集成PHY和控制器,并通过UFS IP解决方案加快产品的上市时间.

验证:使用Verilog HDL编写的测试台在NC-Verilog模拟软件中进行功能验证

功能描述

-

符合JEDEC UFS v3.1的规定

-

向后兼容JEDEC UFS v3.0 & v2.1

-

TAG重叠/LBA重叠/有效的UPIU检查

-

最大的数据输出=64KB

-

最大的数据输入=64KB

-

最大的RTT数=8

-

CMD队列深度=32

-

HW Auto NOP IN Response

-

HW自动查询响应

-

HW 自动写入功能

-

支持HPB v1.0(主机感知性能增强器)。

-

支持EHS(额外头段)

交付件

-

用户手册

-

行为模型和RTL代码

-

测试模式和测试文档

优势

-

写保护选项包括永久保护和通电保护

-

符合RMM标准的可合成RTL设计

-

易于使用的测试环境

应用领域

![]()