概述和功能介绍

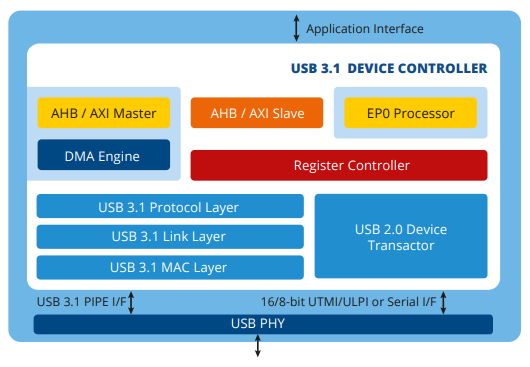

USB 3.1设备控制器是一个高度可配置的核心,并实现了USB 3.1设备的功能,适配第三方USB3.1PHY的接口。USB3.1设备控制器IP是USB3.0系列的一部分。这个设备控制器核心采用高性能DMA引擎,符合USB 3.1规范.

这个控制器内核被精心划分,能够支持标准的电源管理方案,其中包括时钟门控和多个电源井,适配移动和手持设备应用所需的低功耗。这个控制器的应用接口非常简单,可以很容易地适应标准的片上总线接口,如AXI、AHB、OCP以及其他标准的片外互连,易于集成到广泛的应用中。这个控制器IP还有一个专门的PHY Type-C连接器接口,用于识别Type-C的特定功能,如电缆方向、基于配置数据通道的ID功能等.

功能描述

-

符合USB 3.1规范版本1.0

-

实现PHY逻辑/链接/协议层。

-

支持高效的低功耗模式

-

可配置的系统时钟频率

-

支持同时进行的多个IN传输。

-

实现PTM。

-

支持批量流。

-

可配置的管道接口:8、16、32位。

-

灵活的用户应用程序逻辑,其中包括可选的支持EP0处理器的处理控制传输

-

可选的专有DMA控制器。

-

可选的支持

-

支持类型2标题缓冲区

-

支持SCD/LBPM LFPS消息

-

用于内部寄存器访问的简单寄存器接口。

-

支持有关核心特性的各种硬件和软件的可配置性。

-

支持数据、视频和交换机

优势

-

高度模块化和可配置的设计

-

分层体系结构

-

全同步设计

-

同时支持同步和异步重置

-

明显不受干扰的时钟域

-

广泛的时钟门控支持

-

多电源井支持

-

针对关键功能的软件控制

应用领域

-

汽车

-

智能手机

-

片剂

-

笔记本电脑

-

赌博

-

数码相机和摄像机

-

存储

-

无线通信

-

机顶盒

-

智能电视和数字电视

-

芯片对芯片的低功耗互连

交付件

-

可配置的RTL代码

-

基于hdl的测试台和行为模型

-

测试用例

-

协议检查器、总线监视器和性能监视器

-

可配置的合成壳

-

设计指南

-

验证指南

-

合成指南

-

用于预磁带输出验证的FPGA平台

-

参考固件

![]()