DDR PHY IP支持DDR5/DDR4/LPDDR5,延迟性明显降低,并支持高达5400MT/s的吞吐量。PHY的功能可以在NC Verilog仿真软件中使用Verilog HDL编写方式进行的测试验证。Combo PHY IP还可以分别在DDR4、DDR5和LPDDR5模式下运行。

支持的DRAM类型:DDR5/DDR4/LPDDR5

最大控制器时钟频率为675MHz,DDR5的最大DRAM数据速率为5400MT/s

最大控制器时钟频率为400MHz,DDR4的最大DRAM数据速率为3200MT/s

600MHz的最大控制器时钟频率,导致LPDDR5的最大DRAM数据速率为4800MT/s

接口:POD11/POD12/LVSTL05

数据路径宽度以8位增量缩放

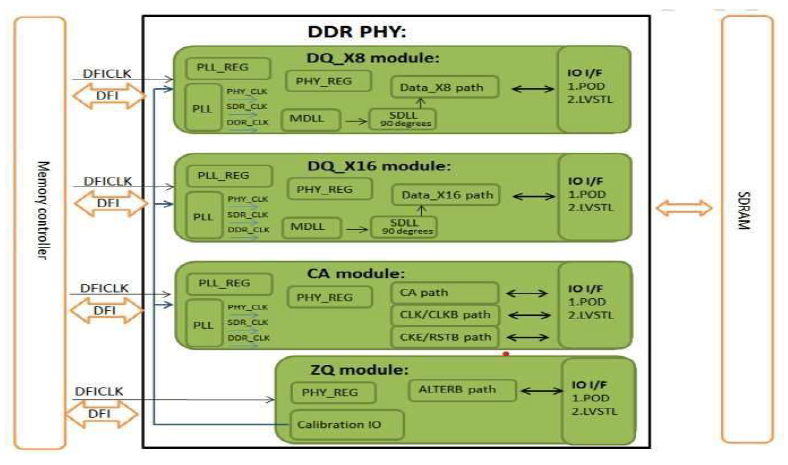

灵活配置的四个模块:

CA/DQ_X16/DQ_X8/ZQ

可编程输出阻抗(DS)

可编程管芯端接(ODT)

核心电源:0.8V,后驱动器电源(VDDQ):1.1V/1.2V/0.5V,前驱动器电源(VDEP):1.1V/1.2V/1.05V

接收器电源(VDDI):1.1V/1.2V/1.05V,适用于DDR5/DDR4/LPDDR5

静电放电:2KV/HBM、200V/MM、500V/CDM

支持ZQ校准

每个CA模块支持4个等级

支持写均衡,CBT

支持PHY内部VREFDQ自动决策

读取和写入数据路径中的每比特去偏移

可交付产品

用户手册

行为模型和受保护的RTL代码

受保护的后布局网表

Synopsys库(LIB)

框架视图(LEF)

金属GDS(GDSII)

测试模式和测试文档