概述和功能介绍

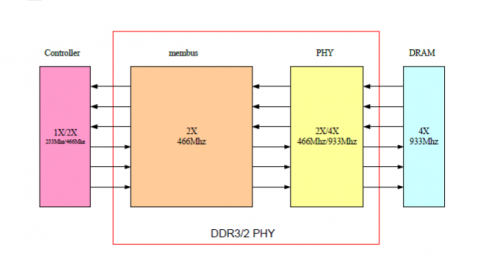

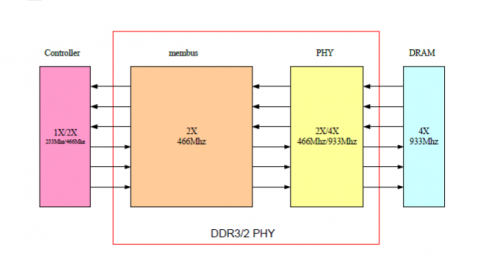

DDR3/2 PHY与JEDEC DDR3和JEDEC DDR2 SDRAM兼容,DDR3模式下DRAM速度为666Mbps~1866Mbps,DDR4模式下DRAM速度为666Mbps~1066Mbps, DDR3/DDR2 SDRAM组件最高支持16个AXI端口,这个设计包括模拟硬宏(CLK/CMD/ADDR/DQ/DQS)和可合成的数字设计。设计支持软件自动训练,包括读门、读/写数据眼计时和PHY Vref设置。DDR3/2 PHY IP通过硅验证具有高性能、低延迟、低面积、低功耗的特性,易于集成在客户的产品中,缩短客户产品研发周期

功能描述

-

支持 DDR3/DDR2 SDRAM

-

DDR3 JEDEC 标准 1.5V I/O(兼容 SSTL_15)

-

DDR2 JEDEC 标准 1.8V I/O(兼容 SSTL_18)

-

16 位宽,单通道 DDR3/DDR2 SDRAM 接口。

-

每通道 16 位,可支持 2 x8 位 DDR3轨道

-

内存时钟频率高达466MHz,DFI时钟频率高达466MHz。

-

支持 DDR3 800/1066/1333/1600/1866Mbps;DDR2 800/1066Mbps

-

支持类似DFI的接口

-

支持连续请求

-

4 位预取架构

-

用于 933MHz 的 DLL 锁定

-

支持软件 DDR 培训

-

支持 DDR IO 环回测试

-

提供每比特去偏斜功能

-

可编程 DQS、DQS# 读/写偏移

-

可编程 CS, MA ,CK/CK#, ODT 偏移

-

支持 DDR3 DLL 禁用模式 (CL6/CWL6)

-

支持 DDR3/DDR2 CL=5 ~ CL17

-

支持 DDR3/DDR2 CWL=5, CWL=11

-

支持 DDR3 读眼训练

-

支持 DDR3 写入眼部训练

-

支持 DDR2 读取门控训练

-

支持 DDR2 读眼训练

-

支持 DDR2 写入眼部训练

-

支持 DDR3 保留模式

-

支持 DQ TX/RX 每位 纠偏

-

0.9V核心电源

-

1.5V DDR3 IO 电源

-

1.8V DDR2 IO 电源

-

支持软件 DDR 培训

-

DDR3 训练:支持 RX_GATED 训练、RX/TX 路径的 perbit 去偏斜、DQ RX 眼部训练和 DQ TX 眼部训练

-

DDR2 训练:支持 RX_GATED 训练、RX/TX 路径的 perbit 去偏斜、DQ RX 眼部训练和 DQ TX 眼部训练

优势

-

每通道 16 位,可支持 2 x8 位 DDR3

-

内存时钟高达 466MHz,DFI 时钟高达 466MHz

-

支持 DDR3 800/1066/1333/1600/1866Mbps;DDR2 800/1066Mbps

-

支持 DDR3 保留模式

-

支持 DDR3 突发长度 4/8

-

支持类似DFI的接口

-

支持连续请求

应用领域

-

固态硬盘控制器

-

数字电视

-

移动

-

多媒体

-

设置框

-

数据中心(网络和存储)

-

服务器

-

高性能计算

-

物联网

-

监控

交付件

-

用户手册

-

行为 模型和受保护的 RTL 代码

-

受保护的帖子布局网表和标准

-

延迟格式 (SDF)

-

帧视图 (LEF)

-

金属GDS (GDSII)

-

测试模式和测试文档