概述和功能介绍

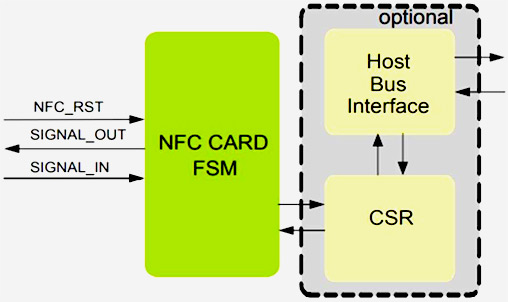

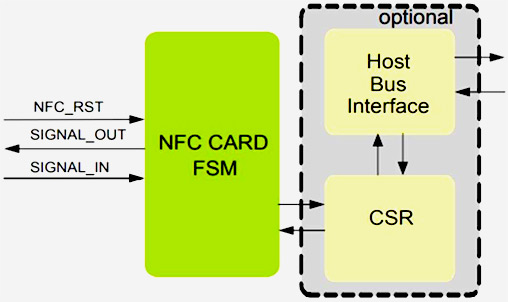

NFC控制器IP功能齐全,易于销售。这个设计可以容易得集成到任何SOC或FPGA开发中,在各种技术中实现。NFC控制器IP符合ISO规范包括ISO/IEC18092、ISO/IEC 14443、ISO/IEC 15693和ECMA 340规范。这个设计还可以支持多种主机总线接口,以便于方便地迁移到不同设计体系结构中,如AHB、AHB-Lite、APB、AXI、AXI-Lite、斜线链、OCP、VCI、Avalon、PLB、Wishbone或自定义总线。NFC CARD IP在Verilog RTL中交付,可以在ASIC或FPGA中实现,可通过使用FPGA测试该NFC控制器IP。其交付件包括RTL代码、测试脚本和一个用于完整仿真的测试环境.

功能描述

-

可在未加密的Verilog、VHDL和SystemC中实现

-

符合NFC规范ISO/IEC 18092、ISO/IEC 14443、ISO/IEC 15693和ECMA 340规范要求。

-

完成NFC控制器PCD/PICC功能。

-

支持半双工制的操作。

-

106 kbps

-

212 kbps

-

424 kbps

-

848 kbps

-

主动通信模式

-

被动通信方式

-

同时支持A型和B型。

-

支持多激活功能,它允许启动器同时激活多个目标。

-

支持链接特性,该特性允许启动器或目标通过将信息划分为几个块来传输不适合单个块的信息

-

防护时间

-

帧延迟时间

-

帧等待时间

-

等待时间延长

-

同步错误

-

DID错误

-

长度错误

-

确认错误

-

无效的命令错误

-

CRC错误

-

奇偶校验错误

-

支持在激活后更改PCD和PICC的参数(传输速度和帧长)

-

完全可合成

-

静态同步设计

-

正边时钟,没有内部三态

-

扫描测试准备就绪

-

简单的接口允许方便地连接到微处理器/微控制器设备

交付件

-

Verilog的RTL设计

-

链接,CDC,合成脚本与豁免文件

-

林特,CDC,合成报告

-

IP-XACT RDL生成的地址映射

-

固件代码和Linux驱动程序包

-

更详细的技术文档

-

易于使用的虚拟机测试环境与虚拟机测试案例