概述和功能介绍

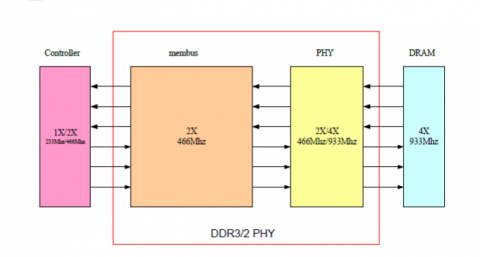

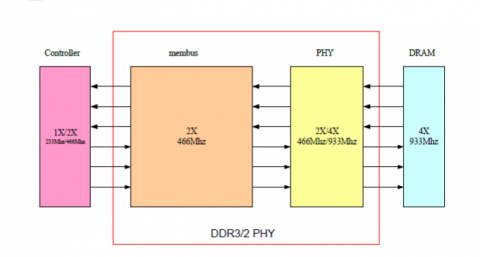

这个DDR PHY IP(双倍数据速率)支持DRAM类型的DDR3、DDR3L。这个PHY可以以最小的延时获得高达1600Mbps的吞吐速率。这个DDR IP符合最新的JEDEC标准,并通过了硅验证。这个PHY IP经过优化,具有高性能、低延迟、低面积、低功率、易于集成的特性,能够帮助客户的产品缩短研发周期更快上市。DDR(双倍数据速率)控制器用于控制DRAM设备,以及访问存储在这些设备上的数据。此外,这个IP还为AXI主站提供多个AXI接口,符合DFI 2.1标准规范,在DDR3/3L模式下传输速率打到800~1600 Mbps、支持X16的设备格式,拥有双等级、写入均衡、数据训练功能和低功耗模式、待机模式。

DDR4/3 PHY IP具有高性能、低延迟、低面积、低功耗的特性,易于集成在客户的产品中,交付件以硬件 DDR PHY 的形式提供,主要以 GDSII 形式交付,包括集成的特定于应用的 DDR4/3 I/O。PHY IP基于RTL 的 PHY,拥有GDSII 的 PHY。DDR4/3 PHY包括一个通往内存控制器的DFI 2.1接口,可以与控制器结合起来,形成一个完整的DDR接口解决方案

.

.

功能描述

-

接口:SSTL

-

最大控制器时钟频率为 400MHz,最大 DRAM 数据速率为 1600Mbps

-

数据路径宽度以 8 位为增量缩放

-

可编程的输出阻抗

-

可编程的输入端接 (ODT)

-

电源:1.1V,I/O 电源:1.5V/1.35V。

-

静电放电 : 2KV

-

支持ZQ校准

-

支持双等级

-

支持 DDR3/3L X16

-

支持写分级

-

工作温度:-40~125C

-

支持低功耗模式、待机模式和保留模式

-

四通道 AXI 和数据宽度 64/128 位

优势

-

DDR3、DDR3L 和 DDR2 SDRAM符合JEDEC 标准规范

-

800 至 1600Mbps 的数据速率

-

基于 GDSII 的“硬件”PHY 避免了基于 “软件” RTL 的 DDR PHY 常见的时序收敛问题

-

包括特定于应用的 DDR I/O ,包括可编程驱动器强度和 ODT

-

符合 DFI 2.1 标准的控制器接口

-

高利用率

-

超低 延迟

应用领域

-

固态硬盘控制器

-

汽车行业

-

应用处理器

-

数字基带调制解调器

-

机顶盒

-

数字电视

-

OTT

-

监控

-

企业级物联网

交付件

-

用户手册/应用说明

-

行为 模型和受保护的 RTL 代码

-

受保护的帖子布局网表和标准延迟格式 (SDF)

-

新思科技图书馆 (LIB)

-

帧视图 (LEF)

-

Hspice 网表 (SP)

-

测试模式和测试文档

.

.