概述和功能介绍

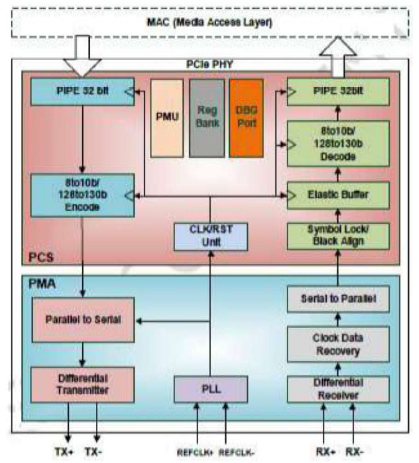

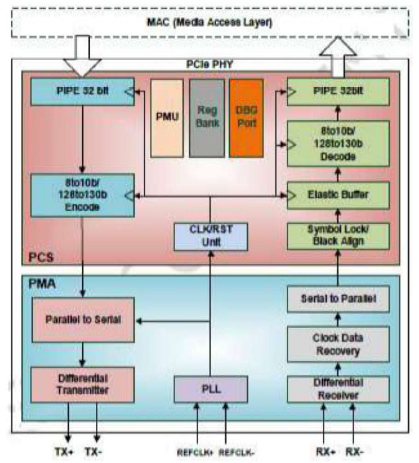

这个PCIe 4.0 PHY IP设计符合PCIe 4.0规范的要求,兼容PIPE 4.4.1接口规范,以低功耗、多通道和高性能为设计目标,支持各种高带宽的传输应用场景。这个PCIe 4.0 PHY IP设计符合PCIe 4.0规范的要求,兼容PIPE 4.4.1接口规范。这个PCIe 4.0 SerDes PHY IP核的数据传输速率可达16Gbps,并兼容PCIe 3.1、PCIe 2.1和PCIe 1.1规范等旧版本所规定的2.5Gbps、5.0Gbps和8.0Gbps速率。PCIe 4.0 IP可以满足各种信道情况下的需要,同时支持TX和RX均衡化方法.

功能描述

-

符合PCIe 4.0基本规范

-

符合PIPE 4.4标准

-

支持的数据传输速率:2.5 GT/s、5.0 GT/s、8.0 GT/s和16.0 GT/s

-

支持的物理通道宽度:X4

-

支持的并行接口。32位

-

支持的输入参考时钟:100 MHz

-

支持的并行接口数据时钟:62.5MHz、125MHz、250MHz和500MHz

-

支持低功耗操作,可在电源状态P1/P2/L1 PM中进行可配置的设置。PLL控制、参考时钟控制和嵌入式电源门控

-

在台积电7纳米工艺中经过硅验证

-

工作电压:0.8V和1.2V

-

通过近端模拟和外部环回接口以及远端模拟/数字环回接口,通过低成本的内置自检(BIST)提

交付件

-

GDSII和层映射

-

位置-路由视图(。LEF)

-

自由库(.lib)

-

Verilog 行为模型

-

Netlist和SDF定时

-

布局指南,应用程序说明

-

LVS/DRC验证报告