概述和功能介绍

The Analog TV Demodulator and Decoder IP core is extracted from a production chip and a silicon-proven IP core. The Analog TV demodulator and decoder are two separate blocks of IP cores available as a single license. The input to the demodulator is digital I/Q LIF or Baseband, the input sample rate is customizable to meet the ADC requirement.

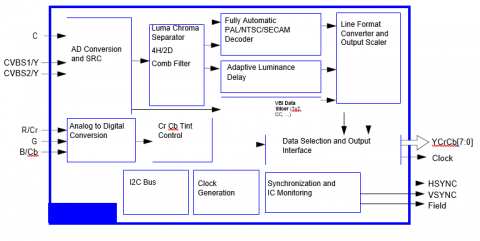

The Analog TV Decoder IP contains a high-quality front-end video circuit for processing all analog NTSC/PAL/SECAM standards into a 4:2:2 YCrCb digital video format as well as conventional analog RGB or YCrCb signals. The programmable through an I²C interface.

The provides a cost-effective solution for digitized TV, LCD TV/monitors, digital TV, STB, video surveillance security, video conferencing, video capturing devices, and PC video card.

The Analog TV Demodulator IP provides support for PAL, NTSC, and SECAM. The all-digital implementation is suitable for integration into digital demodulators and digital SOC devices. The solution covers worldwide TV standards, this IP core block also extracted from production SOC.

The input to the demodulator is digital I/Q at baseband at a 19.33 Msps sample rate. The input sample rate is customizable to meet the requirement and changes to the sample rate will require modifications to the filter chain.

For supporting an IF input, the IF frequency is customizable to meet the requirement. For IF inputs, phase rotation to baseband is accomplished by the “Freq correction” block at left using direct digital frequency synthesis (DDFS).

功能描述

-

Worldwide TV standards compatible

-

Automatic NTSC/PAL/SECAM digital chroma decoder

-

NTSC/PAL adaptive 4H/2D comb filter

-

VBI data slicer for Teletext, closed caption, WSS and other systems

-

Analog RGB/Fast blanking capture and insertion in YCrCb output flow (SCART legacy)

-

Analog YCrCb inputs with tint control

-

10-bit, 30-MSPS ADC for Y/CVBS input

-

8-bit, 30-MSPS ADC for C and RGB/CrCb inputs.

-

Hue control and automatic flesh control for NTSC CVBS/YC signals

-

Programmable horizontal scaling (x0.25 to x4 scaling factor) and panorama vision

-

Copy-protection system compatible

-

H and V synchronisation processing that is robust to non-standard sources such as VCR, and to weak and noisy signals

-

8-bit pixel output interface line-locked ITU-R BT_656/601 or square pixel YCrCb outputs

-

Single system clock for all video input format

-

Two-wire I²C bus interface up to 400 kHz

-

Typical power consumption: 550 mW

-

Power supply: 1.8 V and 3.3 V

-

All-digital Verilog RTL Implementation

-

PAL Support

-

NTSC Support

-

SECAM Support

-

19.33 Msps, 14-bit baseband digital I/Q Input

-

Customized as required

-

Carrier Recovery

-

Vsynch detect to Change Gain Synchronously

-

Rotation to Baseband

-

Raised-Cosine VSB Filter

-

Complex Filtering to Baseband

-

Separation of Video and Audio

-

Audio Filtering High Pass Filter (HPF)

-

Video Filtering Low Pass Filter (LPF)

-

I2C Interface for Configuration

-

19.33 MHz Digital System Clock

-

Customized as required

Benefits

-

Silicon Proven IP core

-

Ready to license with Modifications rights, unlimited usage

-

Pre and post engineering sales support

-

Two separate blocks Demodulator and Decoder

-

Complete package

Applications

-

CRT TVs

-

LCD TVs

-

Digital TV

-

STB

-

Video Capturing Device

-

PC Vdo card

Deliverables

-

Customization: Input sample rate per customer requirementm, Filter modifications per customer requirement and input sample rate Datasheet

-

System Architecture Design Document

-

Synthesizable Verilog RTL

-

RTL Test Bench and Test Vectors

-

Integration Support: Performance Analysis Support, Synthesis and Timing Closure Support

![]()