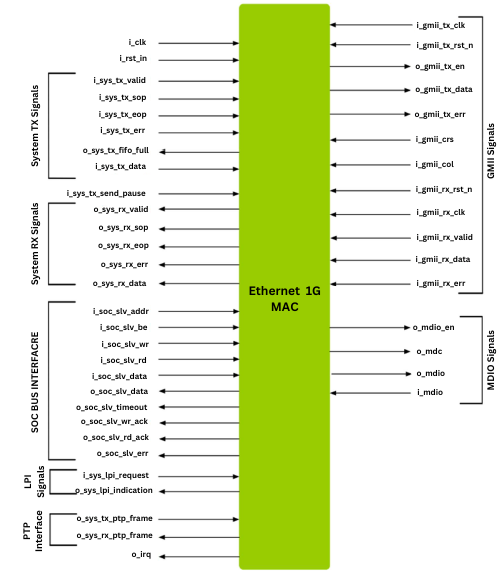

以太网1G MAC IP核心符合IEEE 802.3.2018规范的以太网协议标准,可以无缝集成到任何SoC或FPGA程序中。它可以处理各种主机总线接口,包括AHB、AHB-Lite、APB、AXI、AXI-Lite、Tilelink、OCP、VCI、Avalon、PLB、Wishbone和自定义总线,使其易于集成到任何设计架构中,此外,任何技术都可以用于实现以太网1G MAC IP。以太网1G MAC IP的Verilog RTL实现可以在FPGA和ASIC中找到。利用FPGA对以太网1G MAC IP进行了验证。RTL代码、测试脚本和用于全面模拟的测试环境都包含在核心中。

符合IEEE标准802.3.2018规范

支持全双工和半双工模式

支持GMII和MII接口

支持MDIO(第22条和第45条)接口

支持可编程内部封装间隙(IPG)和前置码长度

根据规范提供详细统计数据

支持IEEE标准802.3az节能以太网(EEE)

支持IEEE标准802.1Q和IEEE标准802.1ad VLAN

支持局域网唤醒

支持环回功能

支持控制框架和巨型框架

支持发送和接收FIFO接口

支持FCS(CRC)传输和接收

支持在全双工模式下暂停基于帧的流量控制

支持系统接口的AXI流接口

内部UNH合规性测试

可选支持TCP/IP

可选支持IEEE标准1588-2008 PTP

可选支持DMA,支持传输和接收端

可选支持RMII、RGMII和TBI接口

完全可合成

静态同步设计

正边缘计时,无内部三态

扫描测试就绪

简单的接口允许轻松连接到微处理器/微控制器设备

可交付成果

Verilog RTL设计

Linting、CDC分析和综合脚本以及弃权文件

Linting、CDC分析和综合报告

IP-XACT RDL生成的地址映射

包含固件代码和Linux驱动程序的软件包

全面的技术文档

Verilog测试环境,提供用户友好的测试用例

优势

完全兼容、经硅验证的核心

配有Verilog测试台和购买全高级系统测试台的选项

直接由设计代码的工程师提供支持

基于RMM(重复使用方法手册指南)

支持所有合成工具