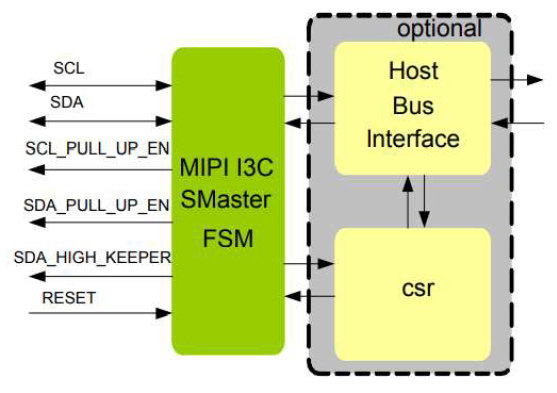

I3C SMaster IP具有完备的功能,能够简单的集成到任何SoC或FPGA的开发中。I3C SMaster IP可以在任意一种技术中实现。I3C SMaster IP符合I3Cv1.1和I3C HCIv1.1规范。此外,这个IP可以支持多种主机总线接口,能够方便地集成到所有设计体系结构中——AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone 或自定义协议等。SMaster IP在Verilog RTL中交付,可以在ASIC或FPGA中实现。SMaster IP通过FPGA的验证,交付件包括RTL代码、测试脚本和用于完整仿真的测试环境.

符合MIPI I3C v1.1和I3C HCI v1.1的规范。

符合JEDEC模块边带总线1.0版规范,具有PEC代码和CCC传输。

符合MCTP I3C Transport Binding 3.0版规范,在从属模式下具有IBI的计数器。

非HCI版本也支持对门数敏感的设计。

完整的MIPI I3C主站、次站和从站功能。

两线串行接口,频率高达 12.5 MHz。

支持所有的拓扑结构--单主-多从-单主-单从-多主-单从-多从-单从-多主-多主-多从

动态寻址,同时支持传统I2C设备的静态寻址。

支持主拉升结构。

支持I3C地址仲裁优化。

支持预测性寻址方案

支持直接命令

支持直接命令CCC构架

支持单数据速率(SDR)信息传递。- 带有直接CCC的SDR - 带有广播CCC的SDR

支持高数据速率(HDR)信息传递 - HDR-双数据速率模式(HDR-DDR) - 带有直接CCC的HDR - 带有广播CCC的HDR - 纯总线模式的HDR-三元符号 - HDR-三元符号遗留的模式

带内中断支持,热连接和二级主控中断支持

带内中断和热连接的自动拒绝功能

Legacy I2C设备在同一总线实例上共存。

Direct数据接口支持(PIO模式) - 用于命令描述符的命令队列 - 用于响应描述符的响应队列 - 用于IBI状态和IBI数据的IBI队列

DMA接口支持(DMA模式) - 单一传输描述符定义命令和数据 - 单一响应状态描述符报告传输的状态 - 链接描述符支持(支持组播消息

交付件

I3C SMaster的IP可以以源代码和网表的形式提供给客户

源代码可以以Verilog语言格式的文本提供给客户,如果客户需要VHDL,SystemC语言格式的文本也可以提供

容易使用的Verilog测试环境及Verilog语言编写的测试用例

Lint、CDC、综合、仿真脚本以及配套的Waiver文件

根据IP-XACT RDL 产生的寄存器地址列表

固件代码和Linux驱动程序包

交付文档包括用户指南和版本手册