概述和功能介绍

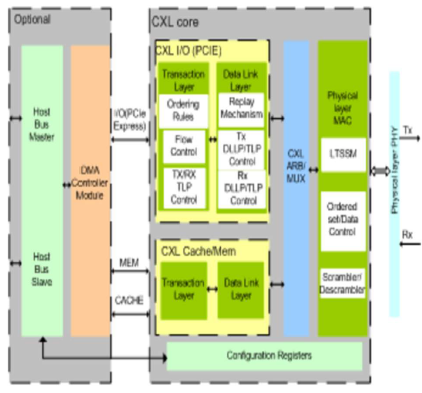

CXL控制器IP设计符合CXL 1.0和1.1规范。CXL控制器IP的兼容功能,通过一个简单的接口得以实现,使它轻易地在各类低成本的设备上展现它的功能。CXL控制器IP在FPGA中可以得到验证。CXL控制器的主机接口可以是简单接口,也可以是AMBA AHB、AMBA AXI、VCI、OCP、Avalon、PLB、Tilelink、Wishbone或自定义协议等等连接方式.

功能描述

-

符合CXL 1.0/1.1规范

-

支持PCIe规范中定义的本机PCIe模式及以下功能•PCIe Express规范1.0/2.0/3.0/4.0/5.0•PIPE接口•完整的PCIe控制器功能•支持ASPM和软件控制的电源管理•支持速度和链路宽度协商•支持上配置、极性反转和通道间偏移

-

支持PCIe与CXL协议模式的静态配置

-

对于CXL模式,支持8 GT/s、16 GT/s或32 GT/s的信号速率

-

支持CXL模式下x16、x8、x4、x2和x1(降级模式)的链路宽度支持

-

在CXL模式下支持x4分支(也称为链路细分)

-

实施CXL。例如CXL。mem和CXL.cache

-

支持ARB/MUX链路管理数据包

-

支持CXL电源管理VDM数据包

-

支持仲裁和数据复用/解复用

-

支持以下CXL.cache/CXL。mem插槽,•标头插槽•通用请求/响应插槽•通用数据插槽

-

支持以下CXL缓存线,•32B半缓存线•64B全缓存线

-

支持以下CXL薄片类型编码,•协议类型•控制类型

-

支持所有CXL.cache/CXL。mem请求和响应消息

-

支持所有窥探响应

-

支持各种帧错误

-

支持多数据头(MDH)

-

支持字节启用

-

支持CXL.cache/CXL。mem链接层重试

-

支持类型1、类型2和类型3 CXL设备

-

支持隐含EDS令牌

-

支持地址转换服务(ATS)

-

支持可配置的TC到VC队列映射

-

支持数据中毒

-

支持虚拟渠道管理

-

支持DMA(可选)

可交付产品

-

CXL控制器接口在源和网表产品中可用。

-

源产品在Verilog中交付。如果需要,还可以提供VHDL、SystemC代码。

-

具有Verilog测试用例的Verilog测试环境易于使用

-

Lint、CDC、合成、模拟脚本以及弃权文件

-

IP-XACT RDL生成的地址映射

-

固件代码和Linux驱动程序包

-

文档包含用户指南和发行说明。

![]()