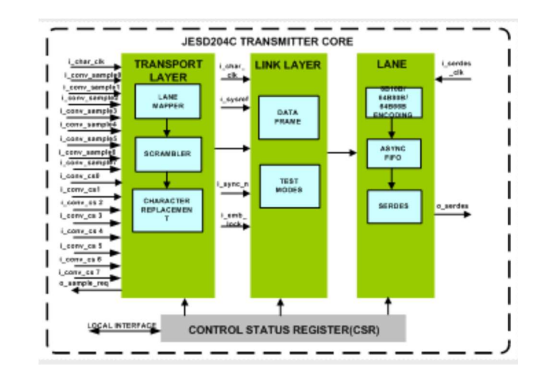

JESD204C接口是一个符合JESD204C.01版本规范的同步串行接口,可以与各种低成本设备进行连接。JESD204C Rx控制器IP已经在FPGA环境中进行了验证。JESD204C的主机接口可以支持多种协议,如AHB、AHB-Lite、APB、AXI、AXI-Lite、Tilelink、Wishbone、OCP、VCI、Avalon、PLB、或自定义协议,也可以是简单的接口。JESD204C发射器IP可以用Verilog或VHDL来描述。

符合JESD204规范JESD204A、JESD204C.01和JESD204C的标准。

完整的JESD204C传输功能。

支持高达32 Gbps的数据速率。

支持可编程时钟频率,最高可达32 GHz。

支持的子类0、1、2。

最高可支持到版本A、B和C。

支持1到8条车道。

每个变送器支持1到8个转换器。

支持每帧1、2、4、8和16个八进制的帧大小。

支持高清模式。

支持每个转换器的1到32位的数据宽度。

支持CF = 0和1每帧时钟周期控制字。

支持每个样本的0到3个控制位。

每个转换器支持1到8个样品。

每组多帧支持1到32帧。

每个示例支持4、8、12、16、20、24、28和32位。

支持0到15个银行ID-扩展到DID。

支持0到255个设备识别号。

支持0到7个车道识别号码。

支持8b/10b编码。

支持64b/66b编码。

支持64b/80b编码。

支持前向误差纠正(FEC)和循环冗余检查(CRC)。

支持单块、多块和扩展的多块。

支持不同的服务器接口10、20、40、60位和自定义位每车道。

扰动抖动模式(JSPAT)和修改的随机模式(修改的RPAT)的连续序列。

用于代码组同步的D21.5或K28.5字符的连续序列。

可以启用或禁用扰频器。

支持MCDA-ML(多转换器设备对齐,多通道)设备。

交付件

JESD204C Tx接口可以以RTL源代码或者网表文件交付

源代码以Verilog语言编写并交付,也可以以提供VHDL,SystemC语言交付

易用的Verilog测试环境及配套Verilog测试用例

Lint、CDC、综合、仿真脚本以及配套的Waiver文件

根据IP-XACT RDL生成的地址映射

固件代码和Linux驱动程序包

文档包含用户指南和发布说明。