概述和功能介绍

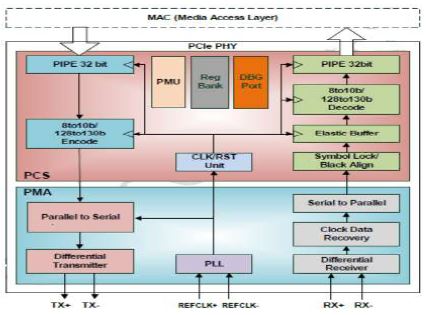

这个外设组件互连快速(PCIe)x4 PHY符合PCIe 5.0基本规范,支持PIPE 5.1接口规范,通过支持额外的PLL控制、参考时钟控制和嵌入式电源门控控制,实现了更低的功耗。此外,这个PHY IP的低功耗模式可以根据不同功耗调整,能够广泛适用于各种场景.

这个PHY IP满足了当今高速芯片芯片、板对板和背板接口的需求,同时具有低功耗和小的工艺尺寸的特点。对于PCIe PHY IP功能的验证能够在NCVerilog模拟软件中使用测试台进行.

功能描述

-

符合PCIe5.0基础规范

-

符合5.1传输管道

-

支持的数据传输速率:2.5 GT/s、5.0 GT/s、8.0 GT/s、16.0 GT/s、32GT/s

-

受支持的物理车道宽度:x4

-

支持的并行接口:16/32位(Gen4/5)、10/20位(Gen1/2/3)

-

支持带有LC储罐的双端口PLL

-

支持CC/SRIS/SRNS

-

支持SSC以减少EMI

-

用于RX-EQ训练的DFE+CTLE

-

用于TX预设的3抽头FFE

-

在L1.2低功耗模式(PMA)下,功率门控实现最低漏电率

-

用于短距离的自动节电

-

TSMC 12纳米FFC 1P10M(ULVT/SVT)工艺

-

工作电压:0.8V和1.2V

-

内置EYE监测器和EYE检查器

优势

-

支持PCIe®5.0、4.0、3.1、2.1、1.1和PIPE规范的所有基础功能

-

支持可分叉的x1、x2、x4、x8、x16的通道配置

-

在L1.2低功率模式(PMA)下,功率门控以达到最低的漏电率

-

低功耗模式(PMA)

-

短距离的自动省电

-

支持的并行接口。16/32-位(Gen4/5),10/20-位(Gen1/2/3)

-

PCIe PHY功能在NCVerilog仿真软件中使用Verilog HDL编写的测试平台进行验证。

应用领域

-

SSD控制器

-

数字电视

-

设置框

-

桌面、工作站、服务器

-

汽车

-

嵌入式系统和机顶盒

-

网络交换机和路由器

-

企业计算和存储网络

交付件

-

应用程序说明/用户手册

-

行为模型和受保护的RTL代码

-

受保护后布局网表和标准延迟格式(SDF)

-

Synopsys库(LIB)

-

框架视图(LEF)

-

金属GDS(GDSII)

-

测试模式和测试文档

![]()