概述和功能介绍

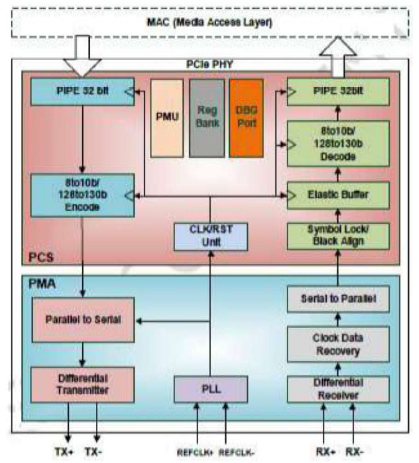

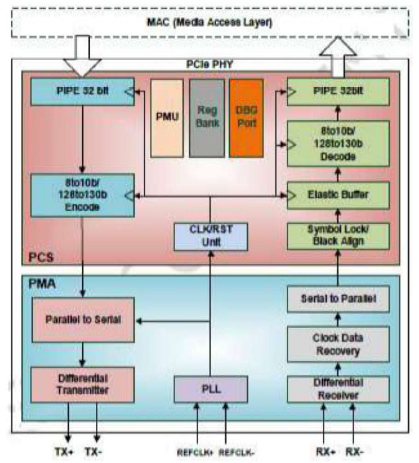

PCIe 2.0 收发器 IP 被广泛地用于各种 PCIe 2.0 Base 应用。 它符合PIPE 3.0 标准。为了能够支持PCIe 2.0 在5Gbps的数据速率并兼容支持PCIe1.0在 2.5Gbps 的数据速率,该设计包含了高速混合信号电路。 它的设计目标旨在追求更低的功耗和更小的面积。PCIe 2.0 IP设计可以均衡支持TX和RX,满足了各种通道环境的需求.

功能描述

-

兼容PCIe基础规范

-

完全兼容PIPE3.0接口规范

-

独立通道断电控制

-

实施接收器均衡 Adaptive-CTLE 以补偿插入损耗

-

支持16位/32位并行接口

-

支持 PCIe gen1(2.5Gbps) 和 PCIe gen2(5.0Gbps)

-

支持灵活的参考时钟频率

-

PCIe模式下支持100MHz差分参考时钟输入或输出(可选择SSC)

-

支持从 -5000ppm 到 0ppm 的扩频时钟 (SSC) 生成和接收

-

支持可编程发射幅度和去加重

-

支持PCIe模式下的TX detect RX功能

-

支持 Beacon 信号生成和检测

-

生产测试支持通过高覆盖率实时 BIST 和环回得到优化

-

集成片上终端电阻和 IO 焊盘/凸块

-

嵌入式初级和次级 ESD 保护

-

ESD:HBM/MM/CDM/闩锁 2000V/200V/500V/100mA

-

在 TSMC 12nm FFC 工艺中通过硅验证

交付件

-

GDSII 和图层图

-

布局布线视图 (.LEF)

-

自由库 (.lib)

-

Verilog 行为模型

-

网表和 SDF 时序

-

布局指南、应用笔记

-

LVS/DRC验证报告