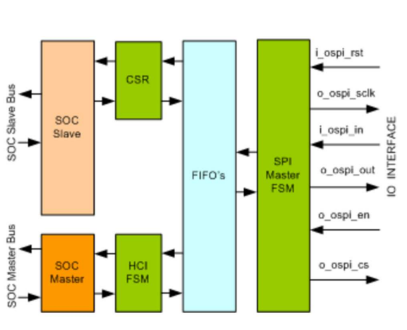

Octal SPI Master控制器IP具备全面的功能,并且操作简便,可与Macronix(MX66LM1G45G)Octal SPI REV.1.0规范兼容。它的八进制SPI接口使其成为广泛应用于低成本设备的理想选择。八进制SPI Master IP在FPGA环境中得到了验证。八进制SPIMaster服务器的主机接口可以支持多种协议,如AMBA APB、AMBA AHB、AMBA AXI、VCI、OCP、Avalon、PLB、Tilelink, Wishbone或自定义协议。

全八进SPI Master功能

快速频率支持(高达133MHz)

符合SPI-事实上的标准

单、双、四、四和八进制串行数据线

软件可编程传输格式(CPOL和CPHA)

在Master控制下支持多达16个奴隶

可配置的SPI传输

针对SPI传输的快速采样时钟输入

符合SPI块规格

用于传输数据的FIFOs(可配置的深度)

全双工操作

LSB或MSB模式

8位、16位、24位和32位同步串行传输

软件可编程SCLK率

支持DMA/HCI(Master机控制器接口)的操作模式。

中断控制

完全可合成

静态同步设计

正边时钟,没有内部三态

扫描测试准备就绪

简单的接口允许方便地连接到微处理器/微控制器设备。

交付件

Octal SPI Master控制器IP可以以RTL源代码或者网表文件交付

源代码以Verilog语言编写并交付,也可以以提供VHDL,SystemC语言交付

易用的Verilog测试环境及配套Verilog测试用例

Lint、CDC、综合、仿真脚本以及配套的Waiver文件

根据IP-XACT RDL生成的地址映射

固件代码和Linux驱动程序包

文档包含用户指南和发布说明。