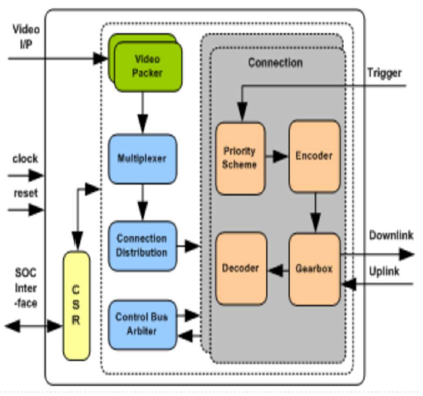

概述和功能介绍

CXP设备IP符合CXP1.1/1.1.1/2.0标准规范。这个IP的兼容性使其为各类低成本设备提供了一个简单的接口。CXP设备IP已在FPGA环境中通过验证。CXP的主机接口可以是简单接口,也可以是AHB、AHB-Lite、APB、AXI、AXI-Lite、Tilelink、OCP、VCI、Avalon、PLB、Wishbone或自定义协议等.

功能描述

-

符合CXP1.1/1.1.1/2.0规范要求。

-

完整的CXP设备功能。

-

支持多达4个连接。

-

支持流通道、输入通道、控制通道

-

支持8、10、12、14、16位深度。

-

高速下行连接的比特率: 1.25 Gbps、2.50 Gbps、3.125 Gbps、5.00 Gbps、6.25 Gbps、10 Gbps、12.5 Gbps

-

低速上行连接的比特率: 20.83 Mbps,41.66 Mbps

-

支持8B/10B编码和10B/8B解码。

-

支持打包CXP v2.0规范所支持的所有视频格式。

-

支持以下颜色格式。•原始•单声道Planar_1到Planar_15 BayerGR,BayerRG,BayerGB,BayerBGRGB•RGBA•YUV_411,YUV_422,YUV_444•YCbCr_601_411,YCbCr_601_422,YCbCr_601_444•YCbCr_709_411,YCbCr_709_422,YCbCr_709_444

-

支持符合CXP v2.0规范的Bootstrap寄存器集。

-

支持来自不同数据流的数据包复用。

-

支持连接测试设施,以测试连接的质量。

-

根据CXP 2.0版规范,支持统一时间戳。

-

支持按照CXP 2.0版规范的链接共享。

-

支持向后兼容1.1.1版本的规范:最大比特率为6.25Gbps的高速连接 ,比特率为20.83Mbps的低速连接,HsUpConnection bootstrap寄存器用于指示HS up连接支持

交付件

-

CXP设备接口可在源代码产品和网络列表产品中使用。

-

源产品以Verilog语言交付。如果需要VHDL格式,还可以提供SystemC代码。

-

容易使用的Verilog测试环境及Verilog语言编写的测试用例

-

链接,CDC,合成,模拟脚本与豁免文件

-

IP-XACT RDL生成的地址映射

-

固件代码和Linux驱动程序包

-

文档包含用户指南和发布说明

![]()