概述和功能介绍

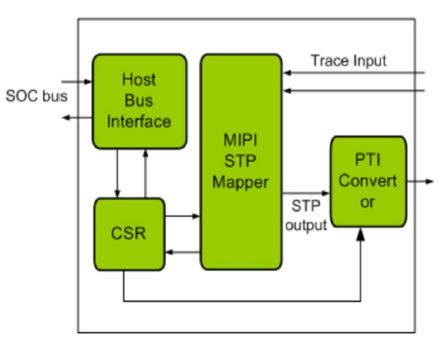

MIPI STP MASTER interface provides full support for the PTI which is a generic high performance parallel interface, support for the two-wire MIPI STP MASTER synchronous serial interface, compatible with MIPI STP specification. Through its MIPI STP MASTER compatibility, it provides a simple interface to a wide range of low-cost devices. MIPI STP MASTER IIP is proven in FPGA environment. It can also support a variety of host bus interfaces for easy adoption into any design architecture - AHB, AHB-Lite, APB, AXI, AXILite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses.

功能描述

-

Compliant with MIPI STP Specification version 2.0 and 2.2.

-

Supports STP interface.

-

Supports ATB interface.

-

Supports Custom interface.

-

Supports a trace stream comprised of 4-bit frames.

-

Supports up to 16 independent data Channels per Master.

-

Supports basic trace data messages that can convey 4, 8, 16, 32, or 64-bit wide data.

-

Supports Time-stamped data packets using one of several time stamp formats including: • Gray code • Natural binary • Natural binary delta • Export buffer depth (legacy STPv1 timestamp that requires DTC support).

-

Supports Data packet markers to indicate packet usage by higher-level protocols.

-

Supports Flag packets for marking points of interest (for higher-level protocols) in the stream.

-

Supports Packets for aligning time stamps from different clock domains.

-

Supports Packets for indicating to the DTC the position of a trigger event, which is typically used to control actions in the DTC.

-

Supports Packets for cross-synchronization events across multiple STP sources.

-

Supports for user-defined data packets.

-

Facilities for synchronizing the trace stream on bit and message boundaries.

-

Fully synthesizable.

-

Static synchronous design.

-

Positive edge clocking and no internal tri-states.

-

Scan test ready.

-

Simple interface allows easy connection to microprocessor/microcontroller devices.

Deliverables

-

The MIPI STP Master interface is available in Source and netlist products.

-

The Source product is delivered in plain text Verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes.

![]()