概述和功能介绍

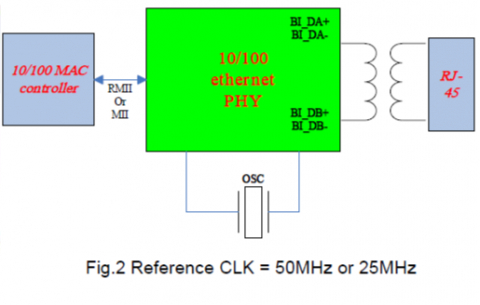

以太网PHY是符合IEEE 802.3u标准的单端口物理层收发器,可以用于10BASE-Te、100BASE-TX操作的低功耗收发器。通过千兆媒体独立接口(GMII),EPHY可以连接到媒体访问控制层(MAC)。在媒体侧,它为100BASE-TX的快速以太网提供与非屏蔽双绞线5类电缆(UTP5)的直接接口,同时也能为10BASE-Te以太网提供UTP5/UTP3电缆的直接接口。以太网PHY采用低功耗和高性能的CMOS工艺。它包含IEEE802.3u标准的100BASE-TX以太网的整个物理层功能,包括物理编码子层(PCS)、物理介质连接层(PMA)、双绞线物理介质相关子层(TP-PMD,仅限在100BASE-TX以太网出现)。因EPHY设计有自动媒体速度/双通道,以及协议选择能力,所以它具备自动协商功能。EPHY还支持Auto MDI/MDIX功能,使网络安装变得便捷

功能描述

-

完全符合IEEE 802.3/802.3u 10BASE-Te、100BASE-TX标准

-

接口符合TP-PMD标准:ANSI X3.263-1995

-

符合FDDI-PMD标准:ISO/IEC 9314-3:1990和ANSI X3.166-1990

-

支持到MAC控制器的GMII接口。

-

符合IEEE 802.3u(MDIO)的串行管理接口

-

支持全双工或半双工操作

-

支持自动协商下一页/并行检测功能

-

符合IEEE 802.3u,也支持手动配置。

-

自动极性校正

-

支持10BASE Te/100BASE-TX的自动MDI/MDIX交叉功能

-

高性能基线漂移校正(BLW)电路

-

高性能数字时钟恢复算法

-

用于ISI缓解的高性能数字均衡器

-

链接、活动、双工、碰撞和速度状态的LED驱动器

-

低功耗设计,支持803.2az标准-2010(EEE)

-

支持MAX 300ppm采样偏移

-

UMC 28nm HPC中的硅+

可交付产品

-

可交付成果

-

详细数据表

-

用于模拟的Verilog行为模型(A)

-

用于合成、STA和等效性检查的Liberty(db./.lib)

-

DFT的CTL/CTLDB

-

ATPG的SPF(标准测试接口语言(STIL)程序文件)

-

4月LEF

-

用于LVS连接的CDL

![]()