12FFC中的DisplayPort v1.4 Tx PHY IP是一种现代化技术,旨在集成到各种设备的芯片设计中,包括图形卡、显示器和笔记本电脑。利用12nm FinFET Compact工艺技术,该IP在功率效率和性能之间取得了平衡,使其成为实现DisplayPort 1.4功能的理想解决方案。使用该DisplayPort 1.4 Tx PHY IP,设备制造商可以在其产品中实现高质量视频和音频信号的无缝传输。这种集成增强了用户的视觉体验,提供了DisplayPort 1.4支持的高级功能和高速数据传输功能。该发射机PHY支持范围广泛的比特率,从1.62Gbps(RBR)到5.4Gbps(HBR2),确保了现代显示技术中的高效数据传输。它包括集成功能,如具有共模偏置的100欧姆终端电阻器,这提高了信号的完整性,并且该发射机PHY包含具有可调强度的集成均衡器,允许在长电缆长度或具有挑战性的环境中进行信号优化。IP还提供可配置的模拟特性,包括CDR带宽、均衡器强度、终端电阻、BGR电压和调节器电压。这种灵活性使定制能够满足特定的要求,并增强了与不同系统配置的兼容性。12FFC中的DisplayPort 1.4 Tx PHY IP在推进显示技术和促进各个行业未来设备的发展方面发挥着至关重要的作用。它与芯片设计的集成使设备制造商能够向用户提供增强的视觉体验,同时保持高效的数据传输能力。

eDP版本1.4a/DP版本1.4兼容变送器

支持HDCP1.4和HDCP2.2(可选)

支持前向纠错(可选)

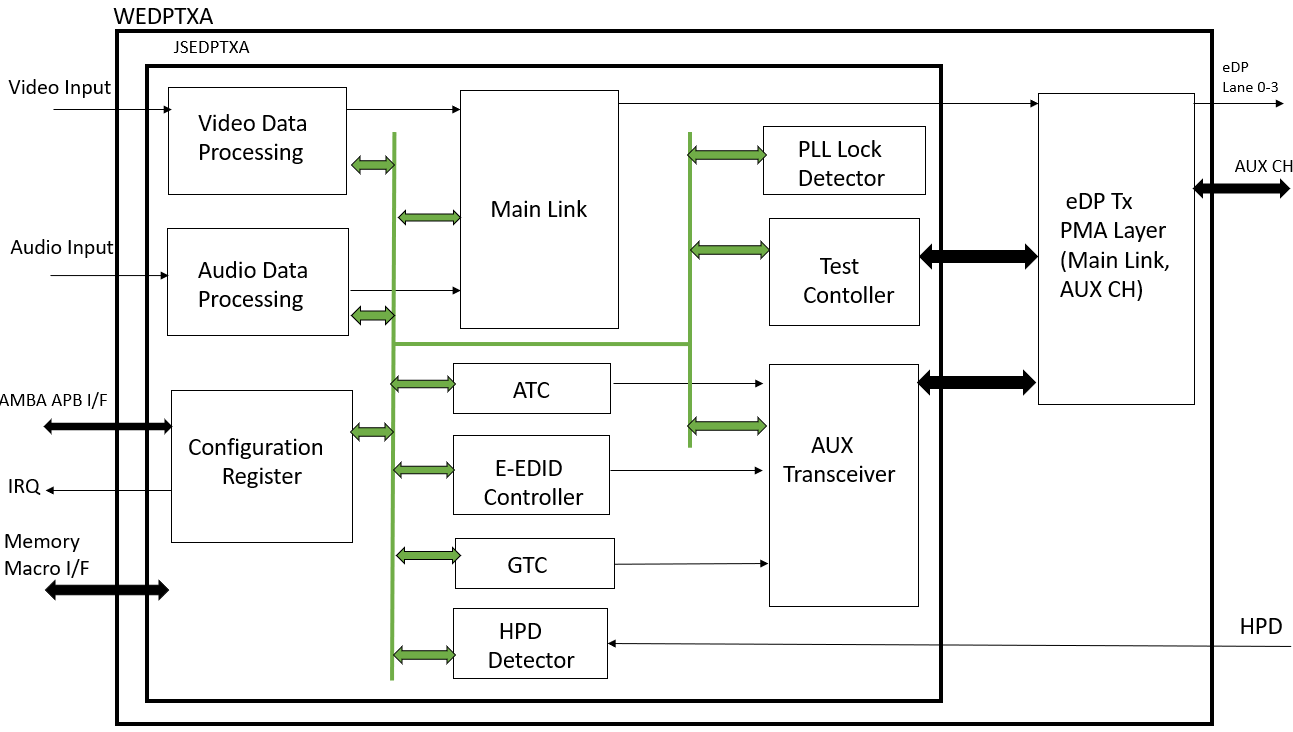

由可配置(4/2/1)链路通道和一个AUX通道组成

支持1.62/2.7/5.4/8.1Gbps(HBR3)比特率和所有推荐的链路速率(即2.16Gbps等)

支持1、2或4车道的主链路运行

同时支持默认和增强帧模式

支持SST模式

支持视频数据包和音频数据包(最大8ch)

支持正常和备用扰频器种子重置

支持通过AUX事务通过I2C读取E-EDID数据

支持视频测试模式生成器(符合DP link CTS v1.2)

可通过AMBA接口编程的配置寄存器

硅在台积电12nm FFC中得到验证

在各种刷新率(60Hz、120Hz、144Hz)下支持高分辨率和刷新率(4K、5K、8K等)。

多流传输(MST)支持连接多个显示器。s.

高动态范围(HDR)支持提高色域和对比度。

节能应用的低功耗。

易于集成的设计,便于集成到半导体芯片或SoC中。

交付件

LINK控制器的Verilog RTL或网表源代码

适用于合成和静态时序分析(STA)的时序抽象模型

综合和物理布局时间限制

行为Verilog模型、模拟测试台、执行脚本和测试刺激

物理设计数据库

集成指南参考软件示例代码