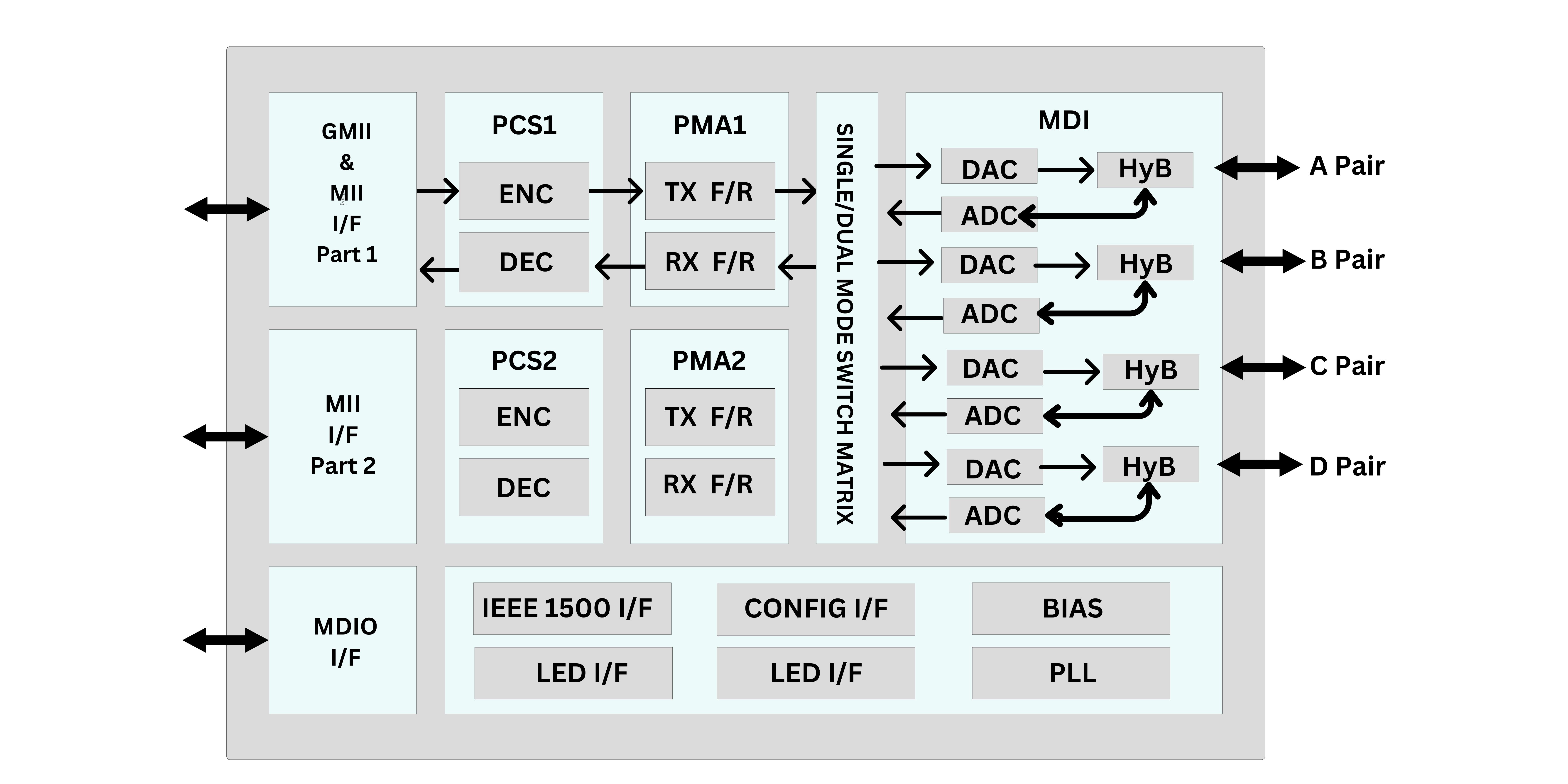

1G以太网PHY IP Core可作为白盒IP进行许可,具有无限使用权和授予客户的完全修改权,确保了可交付成果的高度灵活性。用于Giga 10/100/1000以太网应用的GbE PHY IP是一种高度集成的解决方案,包括双绞线物理介质相关子层(仅限TP-PMD、100BASE-TX)、物理编码子层(PCS)和物理介质连接层(PMA)。它支持10BASE-T、100BASE-TX和1000BASE-T协议,功耗和面积都非常低。媒体访问控制层(MAC)通过GMII(千兆媒体独立接口)或RGMII连接到该GPHY。它支持非屏蔽双绞线5类电缆(UTP5)或UTP5/UTP3电缆。千兆物理层功能由IEEE 802.3ab和IEEE 802.3u定义。

IEEE 802.3-2008,IEEE 802.3az完全符合标准

IEEE 1588-2008支持

BroadR-Reach™支持

双端口MAC接口:

GMII (10/100/1000BASE-T)

MII (10/100BASE-T)

自动协商支持

自动检测和校正对交换(自动MDIX)、对偏斜和对极性

6种不同的操作模式:

1000BASE-T 全双工和半双工

100BASE-TX 全双工和半双工

10BASE-T 全双工和半双工

管理界面

基线漂移补偿

片上发射波形整形

片上混合电路

10KB巨型机架

内部、外部和远程环回

默认操作的硬件配置

断电模式,中断支持

IEEE 1500支持SoC测试集成

LED指示:链路模式、状态、速度、活动和碰撞

从生产芯片组中提取

可交付产品

丰富的产品文档

用于模拟目的的Verilog模型(A)

用于综合、时序分析和等效性验证的自由数据库(.db/.lib)

使用CTL/CTLDB技术进行设计验证

ATPG利用SPF(STIL程序文件)

用于自动地点和路线(APR)的布局交换格式(LEF)

布局与原理图(LVS)对齐的电路描述语言(CDL)t