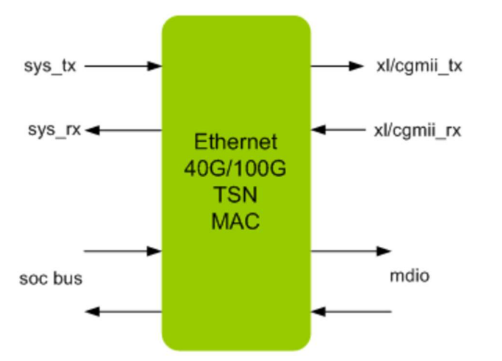

以太网40/100G TSN MAC IP具有完备的功能,能够简单的集成到任何SoC或FPGA的开发中。以太网1G MAC IP可以在任意一种技术中实现。以太网10G XAUI PCS IP符合IEEE 802.3.2018规范中的以太网协议标准。此外,这个IP可以支持多种主机总线接口,能够方便地集成到所有设计体系结构中——AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone 或自定义协议等.

符合IEEE802.3-2018标准的第81条所规定的规范

支持根据IEEE标准802.1Qbu和IEEE标准802.3brr穿插快速流量的预抢占

支持符合IEEE1588-2008(PTP)和IEEE802.1AS(GPTP)标准的定时同步

支持交通调度- IEEE802.1Qbv(增强调度交通)和IEEE802.1Qav(基于信用的塑造)

支持符合IEEE标准802.1Q规范,基于类的流控制和基于类的FIFO来存储每个类,总共8个类

支持全双工操作模式

极低的延迟和小芯片尺寸的实现

支持MDIO(第22条和第45条)接口

支持可编程的填充间隙(IPG)和序言长度

支持XLGMII / CLGMII (64位)接口

支持FCS生成

支持VLAN和巨型帧作为一个选项

独立的TX和RX最大传输装置(MTU)

TSN特性可以独立地启用/禁用

直通式支撑

可配置的传输和接收fifo

综合统计数据收集

支持32位AXI4流的数据包数据

在公司内部进行了UNH的合规性测试

能够轻易地合成到复杂的系统中

静态同步设计

正边时钟,没有内部三态

扫描测试准备就绪

简单的接口能够方便地连接到微处理器/微控制器设备

优势

提供单一站点使用授权提供给在单一站点设计的公司。

提供多站点使用授权提供给在多个站点设计的公司。

单一站点设计技术授权允许在单一的FPGA位流和ASIC中实现IP。

多站点设计技术授权允许在无限数量的FPGA位流和ASIC设计中实现IP

交付件

以太网接口能够在源代码和网路列表产品中使用。

源代码可以以Verilog语言格式的文本提供给客户,如果客户需要VHDL,SystemC语言格式的文本也可以提供

容易使用的Verilog测试环境及Verilog语言编写的测试用例

Lint、CDC、综合、仿真脚本以及配套的Waiver文件

根据IP-XACT RDL 产生的寄存器地址列表

固件代码和Linux驱动程序包

交付文档包括用户指南和版本手册