概述和功能介绍

LPDDR4/ DDR4/ DDR3L 组合 PHY IP 提供低延迟的传输,并支持高达 1866Mbps 的吞吐量。这个PHY IP 通过台积电 28HPC+ 工艺技术的硅验证,符合最新的 JEDEC 规范,专为客户缩短研发周期让产品快速进入市场而设计.

功能描述

-

支持的内存类型:DDR3L/DDR4/LPDDR4

-

最大控制器时钟频率为 400MHz,最大 DRAM 数据速率为 1866Mbps

-

接口: SSTL135/POD12/LVSTL

-

数据路径宽度以 32 位为增量缩放

-

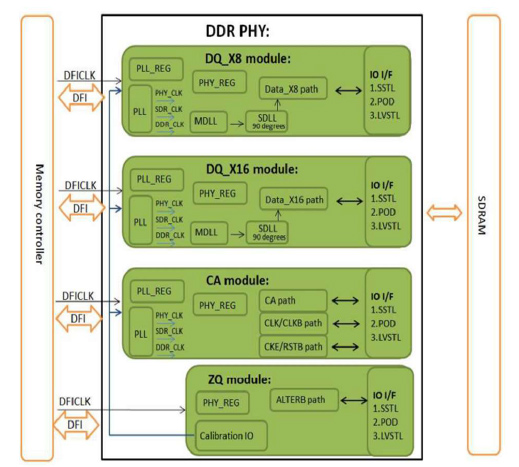

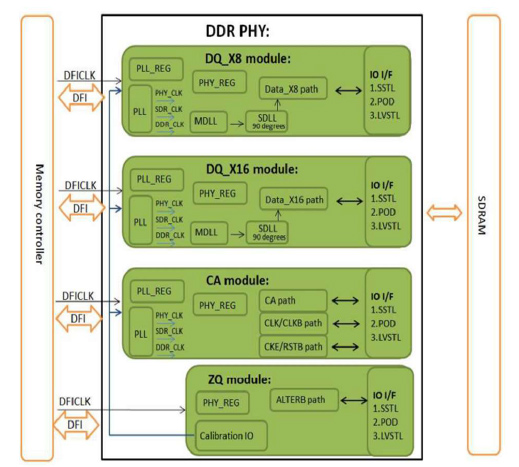

四个模块,配置灵活 :CA/DQ_X16/DQ_X8/ZQ

-

可编程输出阻抗 (DS)

-

可编程片上端接 (ODT)

-

核心电源:0.9V,I/O电源:1.5V/1.35V/1.2V,接收电源:1.8V

-

静电放电: 2KV/HBM, 200V/MM, 500V/CDM

-

支持ZQ校准

-

支持8个等级

-

支持写入均衡、CBT

-

支持物理层内部 VREFDQ 自动决策

-

读写数据路径中的每位纠偏

-

通过台积电 28HPC+ 工艺技术的硅验证

-

支持的金属方案:1P7M_1C

交付件

-

应用说明/用户手册

-

行为 模型和受保护的 RTL 代码

-

受保护的帖子布局网表和标准延迟格式 (SDF)

-

帧视图 (LEF)

-

金属GDS (GDSII)

-

测试模式和测试文档