概述和功能介绍

eDP发射机IP功能齐全,易于销售。这个设计可以容易得集成到任何SOC或FPGA开发中,在各种技术中实现。eDP发射机IP符合ISO规范包括eDP 1.4b规范。这个设计还可以支持多种主机总线接口,以便于方便地迁移到不同设计体系结构中,如AHB、AHB-Lite、APB、AXI、AXI-Lite、 Tilelink、OCP、VCI、Avalon、PLB、Wishbone或自定义总线。eDP发射机IP在Verilog RTL中交付,可以在ASIC或FPGA中实现,可通过使用FPGA测试eDP接收器IP。其交付件包括RTL代码、测试脚本和一个用于完整仿真的测试环境.

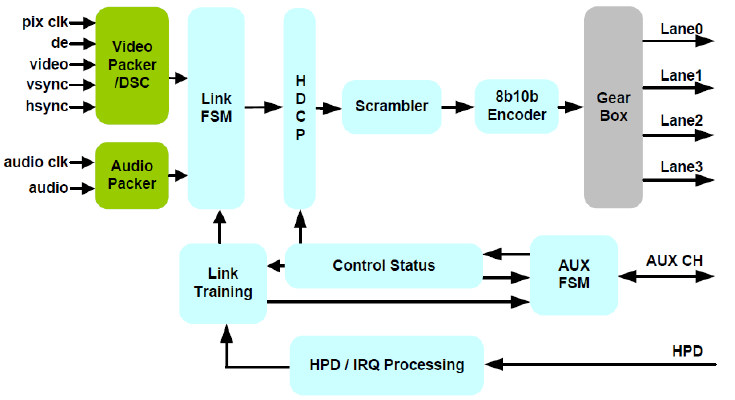

功能描述

-

支持eDP 1.4b规范

-

支持完整的eDP发射器功能

-

支持多通道模式,最多4条通道

-

支持主链路、辅助链路和热插拔功能

-

支持打包显示端口支持的所有视频格式

-

支持基于HPD的链接培训。

-

支持在源模式下的车道间倾斜插入

-

支持显示端口规范中的扰码器

-

支持每隔512个符号后的扰码器复位。

-

支持RGB、YCBCR444、YCBCR422、YCBCR420、Y-Only和RAW颜色格式。

-

支持PSR(面板自刷新)的输入和退出。

-

支持在PSR中的帧号标识。

-

支持面板自更新(PSR)期间的选择性更新(部分帧更新)

-

支持PSR2(面板自刷新)按照规范eDPv1.4b

-

支持多SST操作((MSO)两个SST链路各一车道(共两车道),2x1两个SST链路各两车道(共四车道),2x2四个SST链路各一车道(共四车道),4x1支持高级链路电源管理,以减少唤醒延迟

-

支持基于gtc的视频定时同步

-

支持显示流压缩按照规范eDPv1.4b

-

支持PSR辅助数据包。

-

支持使用DPCD寄存器显示背光控制。支持10位、20位、40位和80位的并行接口

-

支持高带宽数字内容保护系统1.3版(HDCP v1.3)

-

支持高带宽数字内容保护系统版本2.2(HDCP v2.2)支持HDCP2.2与完整的身份验证支持HDCP2.2与绕过身份验证

-

支持高带宽数字内容保护系统2.3版(HDCP v2.3)

-

全可合成、静态同步设计

-

正边时钟,没有内部三态

-

简单的接口允许方便地连接到微处理器/微控制器设备

交付件

-

采用Verilog语言的RTL电路设计

-

Lint、CDC、综合、仿真脚本以及配套的Waiver文件

-

Lint、CDC、综合

-

IP-XACT RDL生成的地址映射。

-

固件代码和Linux驱动程序包。

-

更详细的技术文档。

-

容易使用的Verilog测试环境及Verilog语言编写的测试用例

优势

-

这个IP向后兼容并通过硅验证

-

提供虚拟机测试台,并能够选择购买高级系统虚拟机测试台

-

直接由设计代码的工程师提供支持

-

基于RMM(再使用方法手册指南)

-

支持所有的合成工具

![]()