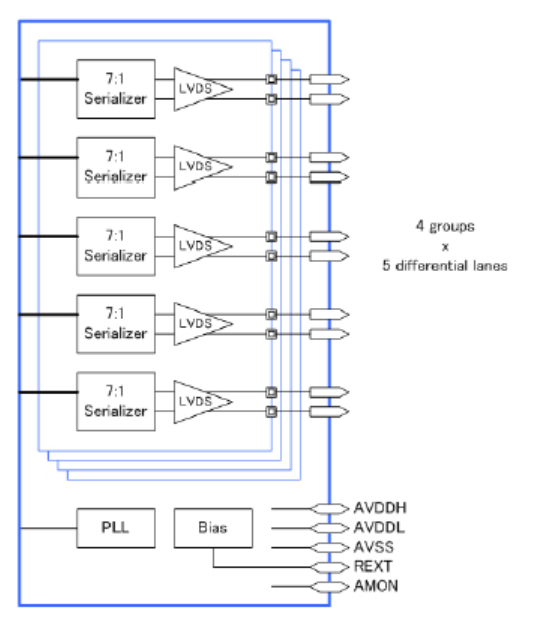

A physical layer IP for LVDS transmitter. This IP consists of 20-lane (4 x 4D1C) LVDS drivers, and supports up to 1.5Gbps data rate.In LVDS mode, both the serial and parallel data are organized into 4 channels. The parallel data is 7 bits wide per channel. The input clock is 25MHz to 150MHz. The serializer is highly integrated and requires no external components. The circuit is designed in a modular fashion and desensitized to process variations. This facilitates process migration, and results in a robust design.

Deliverables