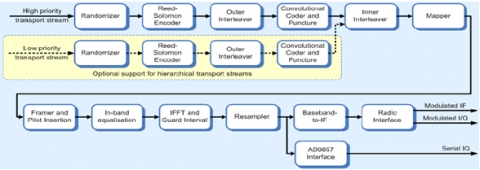

This DVB-T2/T Modulator IP core provides all the necessary processing steps to modulate single transport stream into a complex I/Q signal for input to a pair of DACs, or interpolating DAC devices such as the AD9857/AD9957 or RFDACs such as the AD9789. Optionally the output can be selected as an IF to supply a single DAC. Additional extension cores are available for multiple PLP (common/data) support, T2MI interface support and SFN deployment support. The design has been optimised to provide excellent performance in low cost FPGA devices such as the Cyclone range from Altera or the Spartan range from Xilinx.

A description of the processing steps follows: TS Processing. The TS processing block performs rate adaptation functions in Broadcast applications to ensure that variable transmission delays do not result in disturbances of time-critical services such as audio and video. Both normal-mode and HighEfficiency-Mode(HEM) processing is supported. Null packet deletion. The Null packet deletion block removes null TS packets from the input stream to maximise the capacity available for information services in VCM and ACM modes. The mechanism defined by DVB-T2 allows for complete restoration of the input stream where null packets are necessary to maintain a constant delay. CRC-8 Encoding. An 8-bit CRC is added to each outgoing TS packet and serves to allow packet-level error detection at the receiver. Baseband buffer and Padding. The baseband padding block inserts a fixed-length Baseband Header at the start of each BBFRAME and pads to the end of the frame during ACM operation. The structure of the Baseband Header is as described in EN 302 755. Baseband Scrambling. The baseband scrambler block performs the energy dispersal and transport multiplex adaptation using the DVB randomization polynomial 1+x14+x15. When processing L1-field frames (L1PRE/L1POST), zero padding is added to ensure the non-standard L1 frame length is compliant prior to FEC encoding. BCH, LDPC Encoders. These blocks systematically encode each frame and append error correction information bits. When processing L1-field frames (L1PRE/L1POST), puncturing is performed where necessary following FEC encoding. Bit Interleaver and Demux. The bit interleaver block applies block-based and column-twist bit interleaving to the coded frame prior to symbol demultiplexing and mapping.

Mapping and Rotation. This block performs the QAM constellation mapping using the mapping schemes specified by DVB for BPSK, QPSK, QAM16, QAM64 and QAM256. Optionally constellation rotation is applied as indicated by the L1FIELD information fields, together with L1-ACE modifications when enabledMore detailed info on request, under NDA.