概述和功能介绍

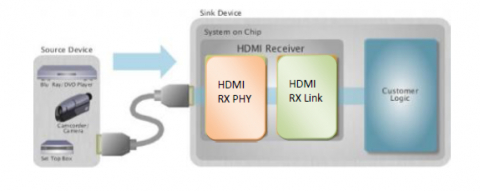

HDMI receiver PHY (Physical layer) IP is single-port core which is fully compliant with HDMI 1.3a specification. This HDMI Rx PHY supports from 25MHz to 225MHz TMDS clock, and offers a simple implementation for system LSI for consumer electronics like HDTV. The HDMI Rx PHY performs most efficiently with HMDI receiver link IP core. It is Silicon Proven in many Fab/Nodes including: (TSMC, UMC, SMIC, GF, Samsung, STMicro). HDMI Receiver Link IP Core supporting the standard of HDMI 1.3a, which will be quickly implemented into SoC of consumers; product (HD-TV, AV receiver... etc.). The best performance, efficiency and characteristic of HDMI Receiver Link IP can be realized when it is connected to HDMI Receiver PHY IP. This HDMI Rx IP can be customized to meet customer specific requirement.

功能描述

-

HDMI version 1.3a compliant receiver

-

Supports DTV from 480i to 1080i/p HD resolution

-

Supports 24bit, 30bit and 36bit color depth per pixel

-

COMPLAINT WITH: HDMI 1.3a, DVI 1.0 , EIA/CEA-861D , HDCP 1.2

-

DIGITAL VIDEO OUTPUT

-

Digital TV resolution - 480i, 576i, 480p, 576p, 720p, 1080i, 1080p

-

PC resolution - VGA, XGA, SXGA, WSXGA, UXGA

-

RGB, YCbCr digital video format

-

12bit RGB/YCbCr 4:4:4

-

16/20/24bit YCbCr 4:2:2

-

8/10/12bit YCbCr 4:2:2 (ITU.601 and 656)

-

Programmable 2-way color space converter

-

YCbCr <-> RGB

-

Deep color supported up to 16bit per pixel

-

Support xvYCC

-

All Packets including Gamut Metadata Packet are receivable

-

DIGITAL AUDIO OUTPUT

-

Standard SPDIF for stereo or compressed audio up to 192KHz

-

PCM, Dolby Digital, DTS Digital Audio transmission through I2s up to 8 channel

-

IEC60958 or IEC61937 compatible

-

DSD (Direct Stream Digital) format for 1 bit Audio/SACD

-

High Bit Rate Compressed Audio (DTS HD master audio/Dolby True digital)

-

CONTENT PROTECTION

-

Built-in High-bandwidth Digital Content Protection (HDCP) encryption engine

-

Authenticate up to 2 receivers and repeaters with maximum cascade of 7

-

Support Advanced Cipher Mode

-

Support Enhanced Link Verification

-

Integrated cable terminator

-

Adaptive equalizer for cable

-

Adjustable analog characteristics

-

PLL band width

-

VCO gain

-

BGR voltage

-

Cable terminator resistance value

-

DLL digital filter characteristics

-

Integrated Audio PLL

-

3.3V/2.5V/1.0V power supply

Deliverables

-

Datasheet

-

Integration guideline

-

GDSII or Phantom GDSII

-

Layer map table

-

CDL netlist for LVS

-

LEF

-

Verilog behavior model

-

Liberty timing model

-

DRC/LVS/ERC results

-

Configurable RTL Code

-

HDL based test bench and behavioral models

-

Test cases

-

Protocol checkers, bus watchers and performance monitors

-

Configurable synthesis shell

-

Documentation

-

Design Guide

-

Verification Guide

-

Synthesis Guide

Benefits

-

Customizable HDMI Rx IP

-

Quick Implementation into the SoC

Applications

-

Digital TV

-

Tablets

-

Mobile phones

-

Digital camera

-

Camcorders

-

Soundbars

-

Audio/Video Receivers

-

DVD players

-

Recorders

-

Streaming-media players

-

Set-top boxes

-

Home theater systems

-

Game consoles

![]()