概述和功能介绍

DisplayPort version 1.4 compliant transmitter PHY supports 1.62Gbps (RBR) to 5.4Gbps (HBR2) bit rate Integrated 100-ohm termination resistors with common-mode biasing Integrated equalizer with tunable strength Configurable analog characteristics CDR bandwidth, Equalizer strength, Terminator resistance, BGR voltage, Regulator voltage, Support PLL test and internal analog signal monitor 1.8V/0.9V power supply.

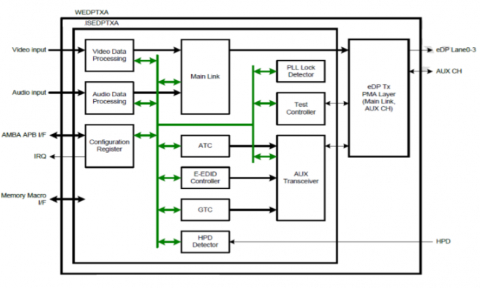

功能描述

-

eDP version 1.4a / DP version 1.4 compliant transmitter

-

Supports HDCP1.4 and HDCP2.2(Optional)

-

Supports Forward Error Correction (Optional)

-

Consists of configurable (4/2/1) link channels and one AUX channel

-

Supports 1.62/2.7/5.4/8.1Gbps (HBR3) bit rate and all recommended link rate (ie 2.16Gbps etc)

-

Supports main link operation with 1 or 2 or 4 lanes

-

Supports both Default and Enhanced Framing Mode

-

Supports SST mode

-

Supports video packet and audio packet (8ch max)

-

Supports both Normal and Alternate Scrambler Seed Reset

-

Supports E-EDID data reading via I2C-over-AUX transaction

-

Supports Video test pattern generator (compliant with DP link CTS v1.2)

-

Configuration registers programmable via AMBA interface

Deliverables

-

Verilog RTL or netlist source code of LINK controller.

-

Abstracted timing models for synthesis and STA

-

Timing constrains for synthesis and physical layout

-

Behavioural Verilog Model, simulation test bench, run control scripts, and test stimuli

-

Physical design database

-

Integration guidelines

-

Reference software sample code

Applications

-

Smart TV

-

Recorders

-

Streaming-media players

-

Home theater systems

![]()