This is an ISDB-T Modulator IP core, which provides all the necessary processing steps to modulate one, two or three transport stream into a complex I/Q signal for input to a pair of DACs, or an interpolating DAC device such as the AD9857/9957 or AD9789. Optionally the output can be selected as an IF to supply a single DAC. The design has been optimized to provide excellent performance in low-cost FPGA devices such as the Cyclone, range from Altera or the Spartan, range from Xilinx.

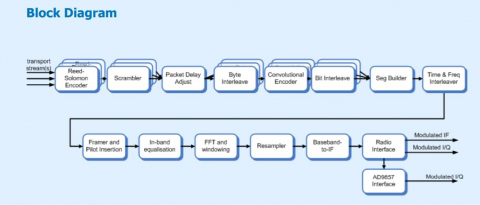

A description of the processing steps follows: Reed-Solomon Encoder. This block generates Reed Solomon packets based on the industry-standard MPEG RS(204, 188) code.

Scrambling: This block provides energy dispersal using the randomization polynomial 1+x14+x15.

Packet Delay Adjustment. Because the different Hierarchical Layers have different delays through the Byte Interleavers, each Layer is delayed to ensure the total delay through the system is an nteger number of frames.

Byte Interleaver. This block performs the outer interleaving function with depth I=12 as specified by the ISDB-T standard. Convolutional Encoder. This block performs convolutional encoding and data-rate puncturing.

Bit Interleaver. This provides additional time dispersal of the signal for improved rejection of impulse noise. Segment Builder. This block formats the hierarchical data for each layer into the specified number of active segments for that layer.

Time Interleaver. This is a long-delay interleaver to spread the information over time to increase immunity to impulse noise.

Frequency Interleaver. The FITL disperses the data over multiple carriers to minimize signal degradation caused by nulls in the frequency response of the transmission environment.

QAM Mapper. This block performs the QAM constellation mapping for (D)QPSK, QAM16, or QAM64.

Framer and Pilot Insertion. The ISDB-T specification details a frame structure with scattered, continuous and TMCC pilots inserted at various carriers within each symbol. This block manages the pilot insertion dependent on the selected mode (2k, 4k or 8k), and symbol position within a frame.

IBEQ. An optional in-band equalizer circuit may be specified as a synthesis option. This allows the designer to easily compensate minor phase and gain slope associated with linear filter components on the board.

IFFT. This block performs the Inverse Fast Fourier Transform (IFFT) on the 2k, 4k or 8k carriers. A proprietary architecture is used which yields low Guassian noise, high MER outputs yet utilizes low datapath widths. The IFFT also manages the on-air timing of the OFDM symbols by guard interval insertion. An optional windowing function is also included to reduce spurious emissions caused by the OFDM symbol transitions.

Resampler. This block resamples the 8.13 MHz complex IFFT output up to complex samples at the core clock frequency. This provides an ultra-flexible clocking strategy. This block also scales automatically as required to satisfy the selected channel bandwidth.

Baseband-to-IF. This block provides the option to mix the signal up to a higher IF as defined by a software register. This block may be removed using synthesis options if it is not required.